Key Takeaways

- Xe3 (Panther Lake) is Intel’s third-generation graphics architecture, focusing heavily on power-constrained mobile and handheld devices.

- Key architectural fixes include a massive L2 cache increase (up to 16MB) and improved register allocation/culling, aimed at stabilizing performance and reducing memory traffic—issues that plagued previous Arc generations.

- XeSS 3 is confirmed, introducing multi-frame generation technology designed to make high-end gaming possible on integrated graphics.

- Early Geekbench results are confusing: a 4-core Xe3 variant performs well (beating the Radeon 840M and GTX 1050 Ti), but other leaks suggest top-tier 12-core variants could rival the RTX 3050, showing massive scaling potential.

- The community is hopeful about the fixes but skeptical of the XeSS 3 image quality claims and anxious about the timeline for the eventual Celestial desktop GPU release.

The Stakes: Why Xe3 is Intel’s Crucial Mobile Comeback

Intel’s forthcoming Panther Lake mobile processors, expected to launch at CES, represent more than just a CPU refresh; they are the proving ground for the Xe3 graphics architecture. Built on Intel’s cutting-edge 18A process, this generation is strategically designed to integrate into thinner, lighter, and more power-efficient devices—specifically targeting the exploding PC gaming handheld market. Xe3 needs to deliver stability and efficiency above all else to succeed in this power-constrained environment. Crucially, this architecture is built upon the hard-won lessons from the first two generations of Arc, focusing on deep architectural fixes rather than just brute-force scaling. If Xe3 fails to deliver reliable, consistent performance, Intel risks falling behind competitors who are already leveraging optimized RDNA 3.5 solutions (like Krackan Point) and increasingly competitive ARM-based silicon from Qualcomm and Apple.

Architectural Deep Dive: Fixing the Arc Foundation

Intel Xe3 Architecture Key Enhancements (Panther Lake iGPU)

- Core Design Basis

- Third-generation Xe Architecture (Xe3)

- Manufacturing Node

- Intel 3 (for initial mobile SKUs)

- Max L2 Cache (iGPU)

- Up to 16MB (in 12-core configuration)

- Ray Tracing

- Updated units with faster bounding-box traversal and larger BVH cache.

- Efficiency Improvement

- Variable Register Allocation and advanced culling for better hardware utilization.

The most critical changes in Xe3 focus acutely on memory and scheduling efficiency. Past Arc GPUs often struggled with high memory traffic and inconsistent core utilization, leading directly to the ‘theoretical throughput vs. actual performance’ gap noted by enthusiasts. Xe3 addresses this head-on by dramatically scaling the L2 cache—up to 16MB in high-end 12-core configurations. This massive cache acts as a critical buffer, significantly reducing the latency associated with accessing system memory, a bottleneck particularly severe in iGPUs. Furthermore, Intel has overhauled register allocation and culling logic. These micro-architectural fixes are designed to ensure the Xe cores are fed data more efficiently and that unnecessary geometry is discarded faster, which is key for smoothing out frame times and eliminating stuttering in complex gaming scenes.

I think it was pretty clear to anyone, that there’s gotta be warp scheduling issues on Arc… Too great of a discrepancy between theoretical throughput and actual performance. Glad they’re fixing that. Anything that threatens the status quo.

The XeSS 3.0 Gambit: Frame Generation for Every Device

XeSS 3 is set to debut alongside Xe3, bringing with it the crucial addition of Multi-Frame Generation. For integrated graphics, frame generation is a fundamental game-changer. Since iGPUs are heavily constrained by power and thermal limits, achieving high native frame rates in modern titles is often impossible. Frame generation allows the GPU to synthesize intermediate frames using AI, dramatically increasing perceived smoothness and responsiveness without requiring proportional increases in rendering power. While the architecture supports this, the community remains intensely skeptical about the resulting image quality, especially given Intel’s lofty claims of generated frames being ‘as good as rendered frames’—a promise that has historically been difficult to achieve without introducing temporal artifacts.

Anya Sharma’s Take: The Quality Question

LoadSyn’s Optimization Science team notes that while XeSS 1.3 delivered significant quality improvements over FSR 2 (especially on the DP4a path), the gap between the latest DLSS 3.7 and XeSS remains measurable. Intel’s claim of ‘rendered quality’ frames must be empirically validated against motion clarity and artifact mapping. The success of Xe3 in handhelds hinges entirely on XeSS 3 delivering truly competitive visual fidelity, otherwise, the architectural performance gains will be negated by a poor user experience.

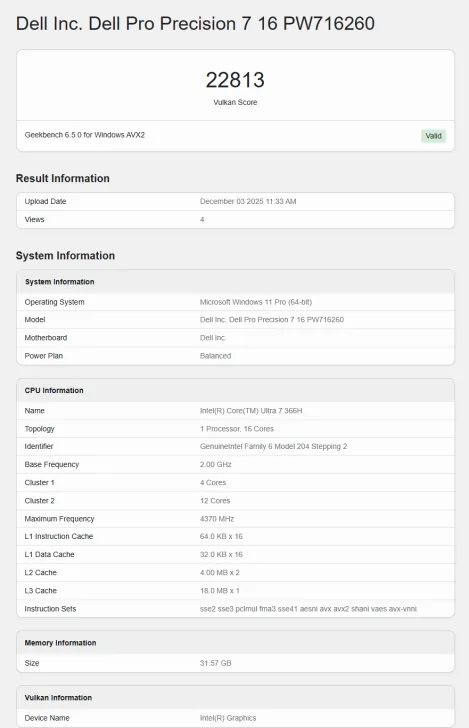

Early Data: Why the Panther Lake Benchmarks Are Confusing

4-Core Xe3 iGPU vs. Integrated & Entry-Level Discrete Competitors (Geekbench Vulkan)

| GPU Model | Core Count | Benchmark Score (Approx.) | Comparative Performance |

|---|---|---|---|

| Intel Xe3 (Core Ultra 7 366H) | 4 Cores | 22,813 | Baseline |

| AMD Radeon 840M (4 CU) | 4 CUs | ~18,100 | 26% Slower |

| NVIDIA GTX 1050 Ti (Mobile) | Discrete | ~22,000 | Trading Blows |

| AMD Radeon 860M (8 CU) | 8 CUs | ~32,000 | 40% Faster |

The initial data from the 4-core Core Ultra 7 366H is indeed a mixed bag, which has sown confusion in the community. The Vulkan score of 22,813 is excellent for a low-core iGPU configuration, proving that Intel has achieved performance parity with the mobile GTX 1050 Ti and significantly surpassed the direct core-count competitor, the Radeon 840M (by 26%). This confirms the architectural fixes are working at the low end. However, this configuration is nearly 40% slower than the high-end 8-core Radeon 860M. The massive performance delta lies in other leaks, such as the Arc B390 (likely a 12-core Xe3 variant), which achieved OpenCL scores suggesting performance between the RTX 3050 and 3050 Ti. This indicates that Xe3’s architectural improvements are highly scalable, but only the top-tier SKUs—those with 10 or 12 Xe cores—will truly deliver the ‘RTX-level’ performance needed to dominate the handheld market. The 4-core model is competitive; the 12-core model promises disruption.

Roadmap Anxiety: What Xe3 Means for the Celestial Desktop GPU

The Xe3 Timeline: From Panther Lake to Celestial

Panther Lake (Xe3) Mobile Launch

Introduction of the architecture and XeSS 3 on laptops and handhelds.

High-Core Xe3 Validation

Top-tier SKUs (10-12 cores) demonstrate RTX 3050-level performance, solidifying the architectural fixes.

Celestial (Xe3 Discrete) Announcement

The first discrete desktop GPUs leveraging the fully scaled Xe3 architecture, potentially built on the 18A process.

Final Verdict: Performance Consistency is Key

Xe3 is Intel’s most important architectural leap since the initial Arc launch. The focus on cache scaling, culling, and register allocation directly targets the performance stability issues that plagued previous generations, signaling a mature design philosophy. If these fundamental fixes hold true, and if the high-core Panther Lake SKUs deliver the RTX 3050-level performance suggested by top-end leaks, Intel will finally establish itself as a dominant force in the mobile and handheld gaming space. The success of Xe3 is not just about raw FPS numbers; it’s about proving that Arc can be consistent and reliable across a broad product stack. The stage is set for a major competitive shift, provided Intel can deliver on the ambitious quality claims of XeSS 3 and maintain a swift pace toward the highly anticipated Celestial desktop debut.